Model sim은 Vivado에서 verilog 코딩 한 뒤에 FPGA에 타켓하기 이전에

시뮬레이션을 하기 위한 용도? 라고 한다.

다양한 회로들을 직접 구현한 뒤에 빠르게 시뮬레이션 돌려서 결과 값을 확인할 수 있다고 한다.

컴퓨터에서 코딩으로 회로를 구현하다 보니 어떠한 스위치와 같은 입력을 주어야 한다.

이것에 대한 역할을 Test bench에서 하게 된다.

전가산기를 예제로 간단하게 모델심을 사용해 보겠다!

Model sim 실행

File -> New -> project

Create Project

Verilog 언어 선택 후 new file 2개 생성

1. (fulladder) test_bench

2. (fulladder) module

전가산기 회로도

[ Full adder.v ]

module fulladd (a, b, ci, sum, co);

input a;

input b;

input ci;

output sum;

output co;

wire w1, w2, w3;

assign w1 = a ^ b;

assign sum = w1 ^ ci;

assign w2 = w1 & ci;

assign w3 = a & b;

assign co = w2 | w3;

endmodule

[ Test_bench.v ]

`timescale 1ns / 1ns // 시간설정 (단위 / 해상도[정밀체크시 ex(1ns/100ps)])

module testbench; // 모듈 선언 및 이름

reg a,b,ci; // 전달받을 데이터를 저장 (계속 사용)

wire sum,co; // 전달받을 데이터를 저장하지않음 (일회성)

fulladd chip_fulladd(a,b,ci,sum,co); // fulladd모듈호출, 호출이름:chip_fulladd

initial // 구문으로 순차적으로 신호를 인가할 때 사용 (한번만 수행)

begin // 구문 시작 {

a=0;b=0;ci=0;#50;

a=0;b=1;ci=0;#50;

a=1;b=0;ci=0;#50;

a=1;b=1;ci=0;#50;

a=0;b=0;ci=1;#50;

a=0;b=1;ci=1;#50;

a=1;b=0;ci=1;#50;

a=1;b=1;ci=1;#50;

end // 구문 종료 }

endmodule // 모듈 종료

베릴로그 코딩 후 컴파일 하여 에러가 없는지 확인

[status]에 V 되었다면 정상!

컴파일 후 [Simulate] 탭에서 [start simulation] !

work -> testbench 선택후 OK!

sim 창이 뜨면 testbench 에서 우클릭 후 Add Wave

중앙 위측에 run 버튼을 통해서 자신이 정한 시간 만큼 파형이 그려진다.

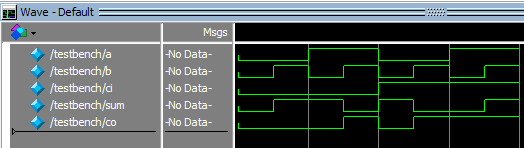

[ 시뮬레이션 결과 그래프 ]