Sequential Logic (순차 논리) 회로란.

출력이 현재의 입력 값에 의해 결정되는 것이 아닌. -> Combination Logic (조합 논리)

과거(기존)의 입력 값(상태)들의 영향 또한 받아서 출력이 결정되는 논리 회로이다.

| combination logic = (+ , - , and, or 과 같은 연산용 로직) sequential logic = 시점에 따라 결과 값이 달라지고, 이를 구성하기 위한 저장매체가 필요하다. |

D 플립플롭은 입력 D의 값을 클럭의 엣지에 캡처해서 Q에 반영한다. (값을 저장)

D 플립플롭의 출력 상태 변화는 클럭의 엣지에서만 이루어진다.

즉, 클럭에 동기화 되어 출력의 상태 변화가 일어난다.

SET, RESET 에 의해서 값을 클럭에 비동기하여 초기화가 가능하다.

| Clock | D | Q |

| 상승 엣지 | 0 | 0 |

| 상승 엣지 | 1 | 1 |

| 엣지 없음 | X | Q |

진행환경 & 사용 툴

- windows 10 환경

- Quartus prime Lite Edition (17.1 ver)

- Model sim (10.5b ver)

< d_ff.v >

module d_ff(clk, rstn, i_value, o_value);

output reg [1:0] o_value;

input [1:0] i_value;

input clk, rstn;

always @(posedge clk or negedge rstn)

if(!rstn)

o_value <= 0;

else

o_value <= i_value;

endmodule

< tb_d_ff.v >

`timescale 1ns/1ps

module tb_d_ff();

reg clk,rstn;

reg [1:0] i_value;

wire [1:0] o_value;

initial

begin

clk = 0;

rstn = 0; #100;

rstn = 1;

end

always @ (posedge clk or negedge rstn) begin

if(!rstn)

i_value = 0;

else

i_value = i_value +1;

end

always #50 clk = ~clk;

d_ff tb_d_ff(

.clk (clk),

.rstn (rstn),

.i_value (i_value),

.o_value (o_value)

);

endmodule

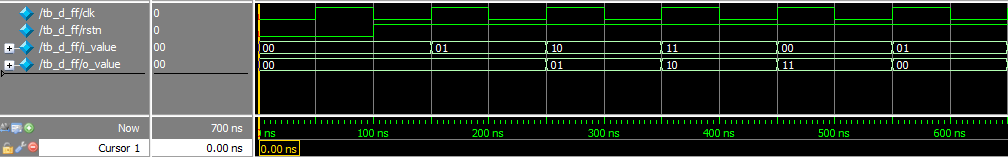

시뮬레이션 결과

정상적으로 out value의 값이 input value의 다음 CLK의 상승엣지에 맞춰 출력 됨을 볼 수 있다.

'FPGA > Verilog study' 카테고리의 다른 글

| [Verilog HDL] 1. 수의 표현 (0) | 2021.08.10 |

|---|---|

| [Verilog] 클럭 나눠서 원하는 시간 맞추기 (clock division) (0) | 2021.05.17 |

| [Verilog] FSM 설계 스탑워치 구현 (0) | 2021.05.17 |